# **IpGBT Documentation**

Release

**IpGBT Design Team**

# **CONTENTS**

| 1 | Intro | troduction 3                                                            |  |  |  |  |  |  |

|---|-------|-------------------------------------------------------------------------|--|--|--|--|--|--|

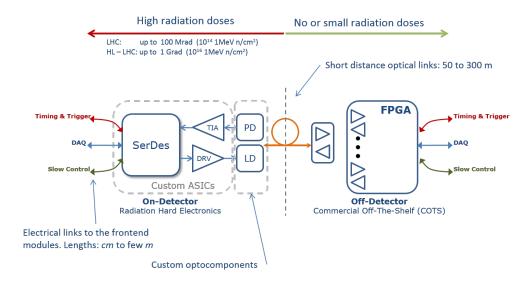

|   | 1.1   | Radiation Environment                                                   |  |  |  |  |  |  |

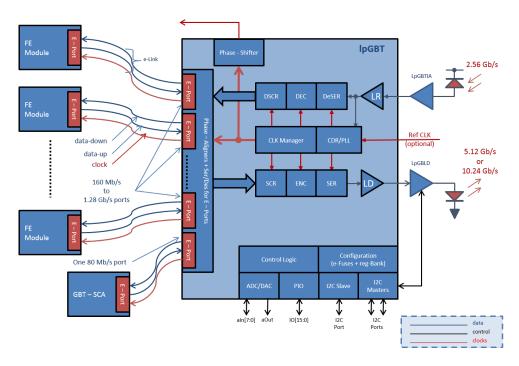

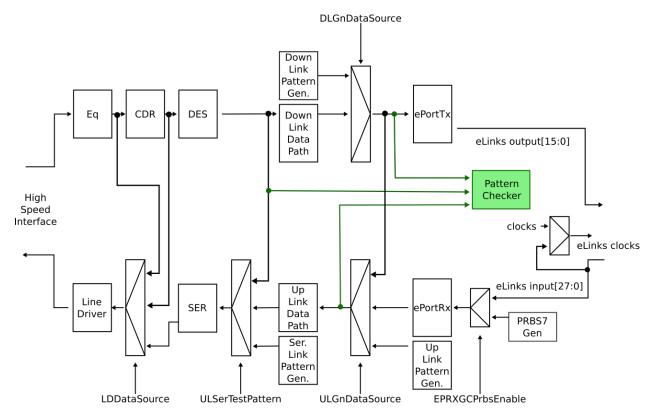

|   | 1.2   | Architecture and Functionality Overview                                 |  |  |  |  |  |  |

|   |       | 1.2.1 Down and Up Optical Links                                         |  |  |  |  |  |  |

|   |       | 1.2.2 Electrical Links (eLinks)                                         |  |  |  |  |  |  |

|   |       | 1.2.3 ePorts                                                            |  |  |  |  |  |  |

|   |       | 1.2.4 ePorts Output/Input Phases                                        |  |  |  |  |  |  |

|   |       | 1.2.5 ePort Drivers and Receivers                                       |  |  |  |  |  |  |

|   |       | 1.2.6 ASIC Control                                                      |  |  |  |  |  |  |

|   |       | 1.2.7 Experiment Control and Monitoring                                 |  |  |  |  |  |  |

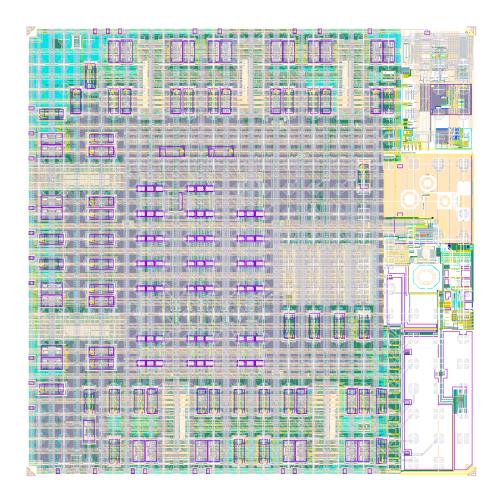

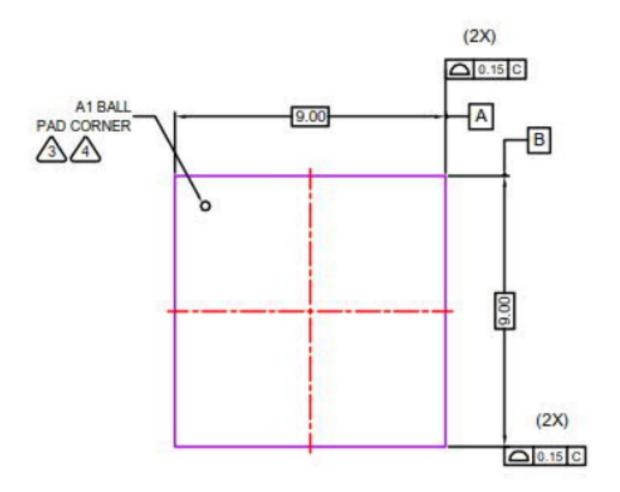

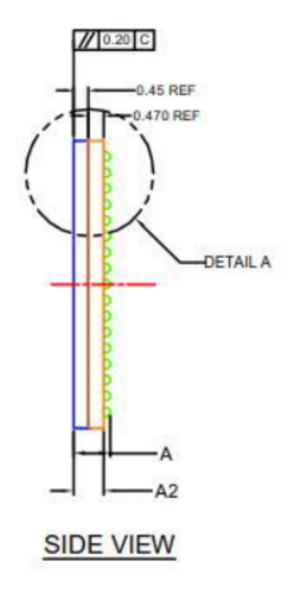

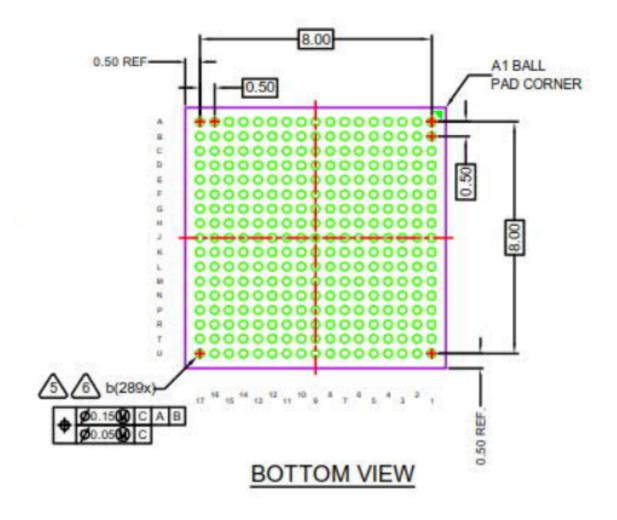

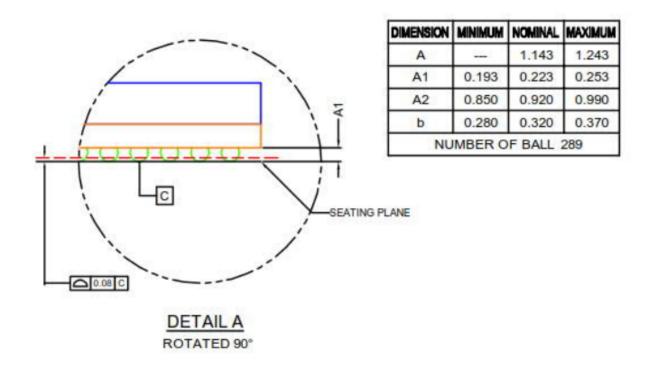

|   |       | 1.2.8 ASIC Package                                                      |  |  |  |  |  |  |

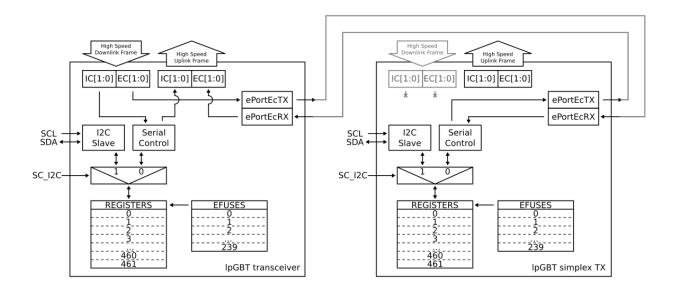

|   | 1.3   | Transceiver modes                                                       |  |  |  |  |  |  |

|   | 1.5   | 1.3.1 Simplex transmitter                                               |  |  |  |  |  |  |

|   |       | 1.3.2 Simplex receiver                                                  |  |  |  |  |  |  |

|   |       | 1.3.3 Transceiver                                                       |  |  |  |  |  |  |

|   |       | 1.5.5 Transceiver                                                       |  |  |  |  |  |  |

| 2 | Quicl | start                                                                   |  |  |  |  |  |  |

|   | 2.1   | Configuration pins                                                      |  |  |  |  |  |  |

|   | 2.2   | Configuration registers                                                 |  |  |  |  |  |  |

|   |       | 2.2.1 Clock generator registers                                         |  |  |  |  |  |  |

|   |       | 2.2.2 Uplink: ePort Inputs DLL's                                        |  |  |  |  |  |  |

|   |       | 2.2.3 Uplink: Line driver settings (if high speed transmitter is used)  |  |  |  |  |  |  |

|   |       | 2.2.4 Uplink: ePort Inputs Group 0 at 1.28 Gbps                         |  |  |  |  |  |  |

|   |       | 2.2.5 Uplink: ePort Inputs Group 1 at 640 Mbps                          |  |  |  |  |  |  |

|   |       | 2.2.6 Downlink: Frame aligner settings (if high speed receiver is used) |  |  |  |  |  |  |

|   |       | 2.2.7 Downlink: ePort Outputs Group 0 at 320Mbps                        |  |  |  |  |  |  |

|   |       | 2.2.8 Downlink: ePort Outputs Group 3 at 80Mbps                         |  |  |  |  |  |  |

|   |       | 2.2.9 eLink clocks                                                      |  |  |  |  |  |  |

|   |       | 2.2.10 Phase-shifter clocks                                             |  |  |  |  |  |  |

|   |       | 2.2.11 Finishing configuration                                          |  |  |  |  |  |  |

|   |       |                                                                         |  |  |  |  |  |  |

| 3 | Confi | guration 17                                                             |  |  |  |  |  |  |

|   | 3.1   | Configuration pins                                                      |  |  |  |  |  |  |

|   |       | 3.1.1 MODE3, MODE2, MODE1, MODE0                                        |  |  |  |  |  |  |

|   |       | 3.1.2 SC_I2C                                                            |  |  |  |  |  |  |

|   |       | 3.1.3 ADR3, ADR2, ADR1, ADR0                                            |  |  |  |  |  |  |

|   | 3.2   | Register access                                                         |  |  |  |  |  |  |

|   | 3.3   | Chip Address                                                            |  |  |  |  |  |  |

|   | 3.4   | Serial control and monitoring interface                                 |  |  |  |  |  |  |

|   | 3.5   | I2C slave interface                                                     |  |  |  |  |  |  |

|   |       |                                                                         |  |  |  |  |  |  |

|   |        | 3.5.1 Write to Register                                          | 22 |

|---|--------|------------------------------------------------------------------|----|

|   |        | 3.5.2 Read from Register                                         | 23 |

|   | 3.6    | E-FUSES                                                          | 23 |

|   |        | 3.6.1 E-fuse power                                               | 23 |

|   |        | 3.6.2 E-fuse addressing                                          | 24 |

|   |        | 3.6.3 E-fuse programming                                         |    |

|   |        | 3.6.4 E-fuse reading                                             |    |

|   | 3.7    | Configuration flows                                              |    |

|   | 3.7    | 3.7.1 Complete configuration stored in fuses                     |    |

|   |        | 3.7.2 Configuration over I2C                                     |    |

|   |        | 3.7.3 Using serial control channel                               |    |

|   |        | 5.7.5 Using serial control channel                               | 20 |

| 4 | High   | speed links                                                      | 27 |

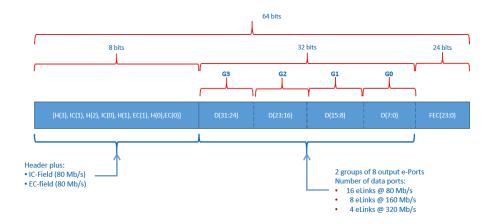

| • | 4.1    | Downlink frame                                                   |    |

|   | 1.1    | 4.1.1 Frame format                                               |    |

|   |        | 4.1.2 Forward error correction                                   |    |

|   |        | 4.1.3 De-scrambling (and scrambling)                             |    |

|   |        | 4.1.4 De-interleaving (and interleaving)                         |    |

|   |        |                                                                  |    |

|   |        | TI 8                                                             |    |

|   | 4.0    | 4.1.6 Frame alignment and fixed latency                          |    |

|   | 4.2    | Uplink frames                                                    |    |

|   |        | 4.2.1 Frame formats                                              |    |

|   |        | 4.2.2 Scrambling                                                 |    |

|   |        | 4.2.3 Forward Error Correction                                   |    |

|   |        | 4.2.4 Interleaving                                               |    |

|   | 4.3    | High speed links polarity                                        | 35 |

| _ | TT! 1  |                                                                  | 20 |

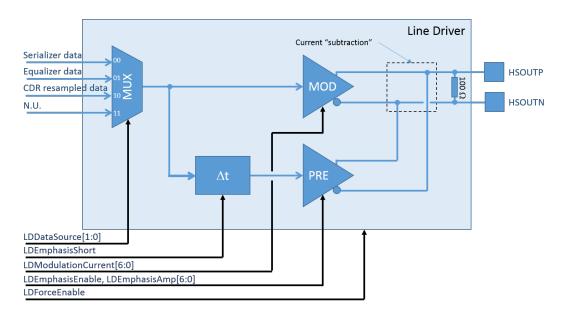

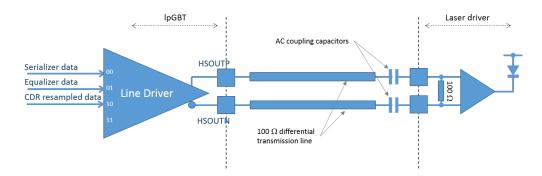

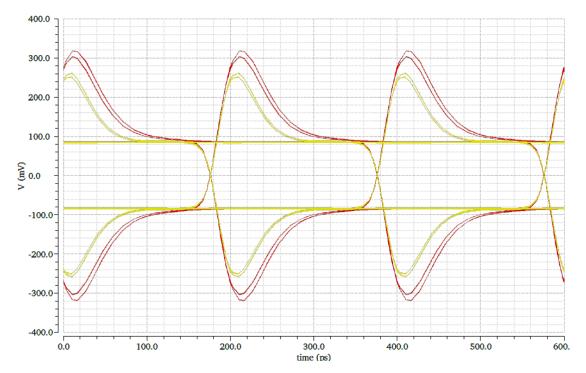

| 5 | _      | -Speed Line Driver                                               | 39 |

|   | 5.1    | Line driver functionality                                        |    |

|   |        | 5.1.1 Input multiplexer                                          |    |

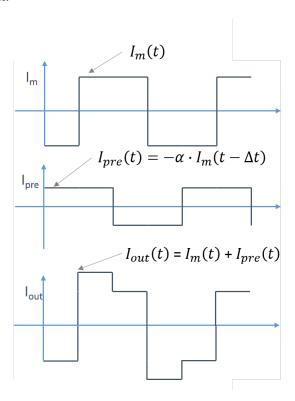

|   |        | 5.1.2 Modulation and pre-emphasis                                | 40 |

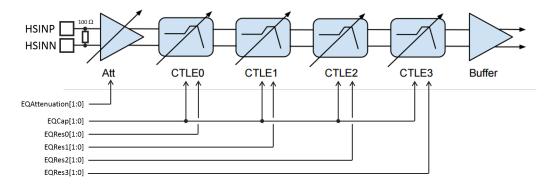

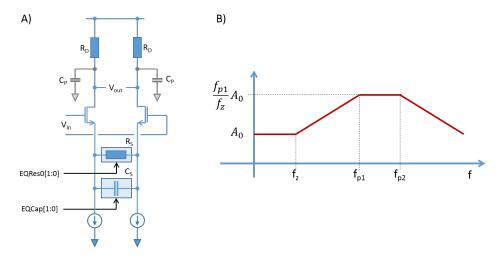

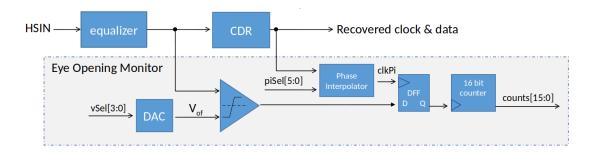

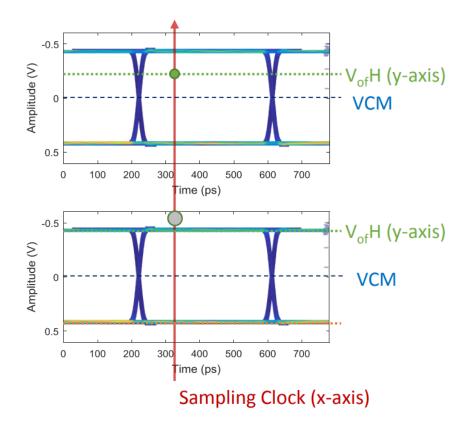

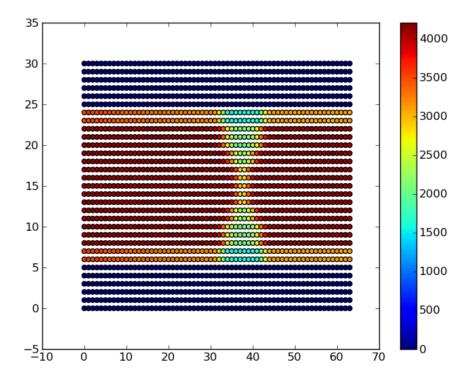

| 6 | High   | -Speed Equalizer                                                 | 43 |

| U | riigii | -speed Equalizer                                                 | 4. |

| 7 | Elect  | trical links                                                     | 47 |

| • | 7.1    | eLink Groups                                                     |    |

|   | 7.2    | eLink pin naming conventions.                                    |    |

|   | 7.3    | eLink Tx Mirror function                                         |    |

|   | 7.4    | eLink Clocks                                                     |    |

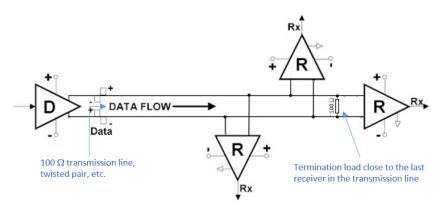

|   | 7.5    | CERN Low Power signalling (CLPS)                                 |    |

|   |        |                                                                  |    |

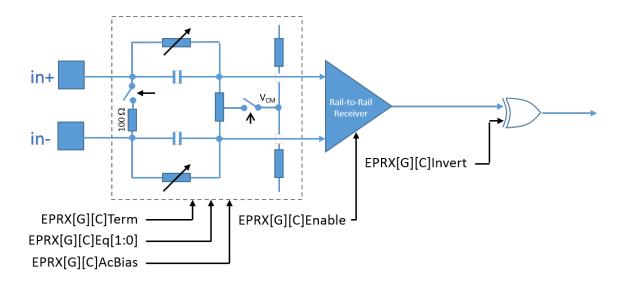

|   | 7.6    | eLink Receivers (eRx)                                            |    |

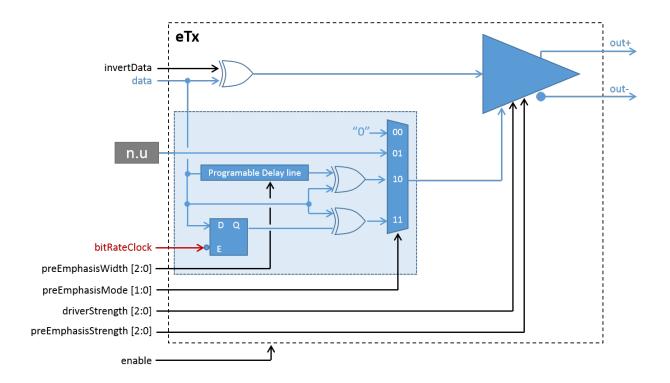

|   | 7.7    | eLink Drivers (eTx)                                              |    |

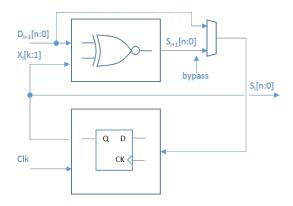

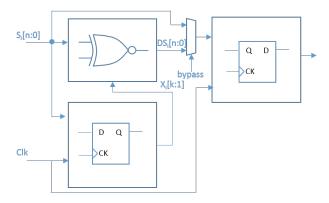

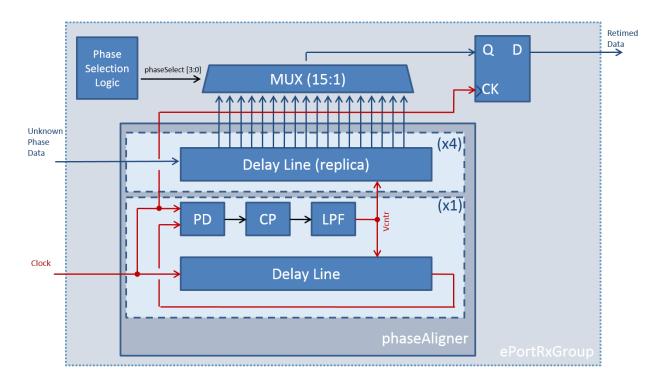

|   | 7.8    | Phase alignment                                                  |    |

|   |        | 7.8.1 Downlink phase alignment                                   |    |

|   |        | 7.8.2 Uplink phase alignment                                     |    |

|   |        | 7.8.3 ePortRx group DLL programming                              |    |

|   |        | 7.8.4 Note about DC balancing and data/clock encoding for eLinks |    |

|   | 7.9    | eClocks Wrap-up                                                  |    |

|   | 7.10   | Uplink eLinks (inputs) Wrap-up                                   |    |

|   | 7.11   | Downlink eLinks (outputs) Wrap-up                                | 60 |

| n | G4 4   | Company de manda la de la                                        | ~- |

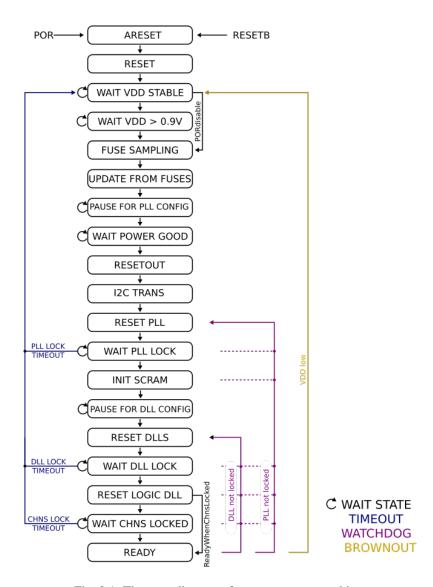

| 8 |        | t-up and watchdog                                                | 61 |

|   | 8.1    | Power-up state machine                                           |    |

|   | 8.2    | Power-on reset                                                   |    |

|   | 8.3    | Timeout feature                                                  | 64 |

|    | 8.4                                                                                         | Watchdog operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65                                                                                                             |

|----|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|    |                                                                                             | 8.4.1 Notes on using the watchdog in an SEU environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                                                                                                             |

|    | 8.5                                                                                         | Brownout detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                                                             |

|    | 8.6                                                                                         | Disabling the power-up sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 66                                                                                                             |

|    | 8.7                                                                                         | Configuration pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67                                                                                                             |

|    |                                                                                             | 8.7.1 STATEOVRD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67                                                                                                             |

|    |                                                                                             | 8.7.2 PORDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                                                                                                             |

|    |                                                                                             | 8.7.3 RSTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67                                                                                                             |

|    |                                                                                             | 8.7.4 READY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                                                                             |

|    |                                                                                             | 8.7.5 RSTOUTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                                             |

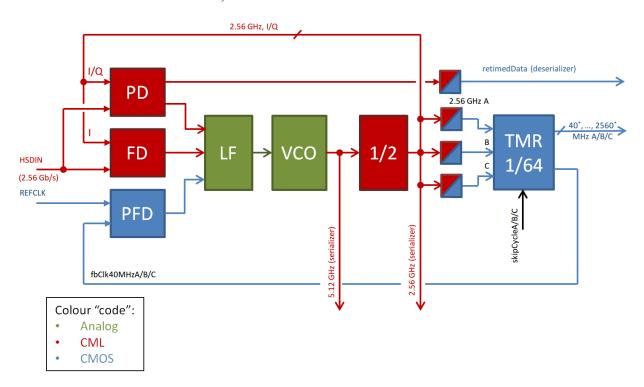

| 9  | Clock                                                                                       | k Generator Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 69                                                                                                             |

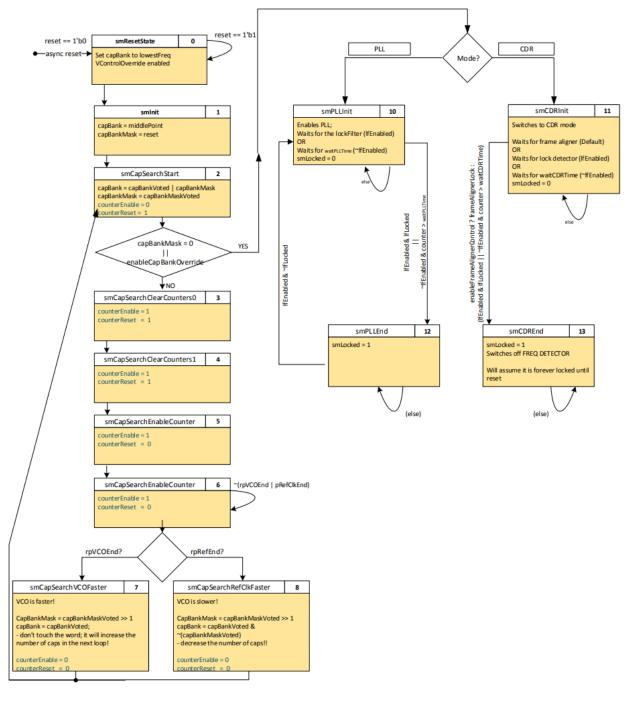

|    | 9.1                                                                                         | Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 70                                                                                                             |

|    | J.1                                                                                         | 9.1.1 VCO calibration in PLL mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70                                                                                                             |

|    |                                                                                             | 9.1.2 VCO calibration in CDR mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                             |

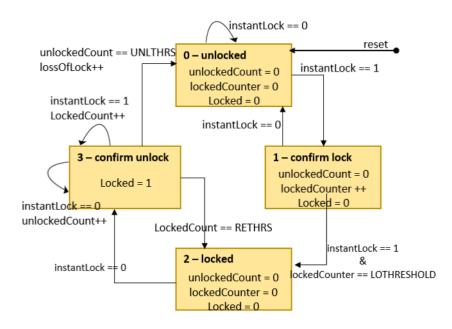

|    | 9.2                                                                                         | Lock detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                                                                                             |

|    |                                                                                             | 9.2.1 PLL mode - lock filter lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                             |

|    |                                                                                             | 9.2.2 CDR mode - frame aligner lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                                             |

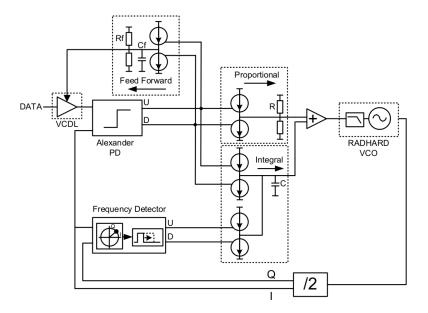

|    | 9.3                                                                                         | Loop control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                                             |

|    |                                                                                             | 9.3.1 PLL loop control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 73                                                                                                             |

|    |                                                                                             | 9.3.2 CDR loop control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74                                                                                                             |

|    | 9.4                                                                                         | Configuration and clock pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                             |

|    |                                                                                             | 9.4.1 REFCLKP and REFCLKN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75                                                                                                             |

|    |                                                                                             | 9.4.2 TSTCLKINP and TSTCLKINN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                                                                                             |

|    |                                                                                             | 9.4.3 LOCKMODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75                                                                                                             |

|    | 9.5                                                                                         | VCOBYPASS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76                                                                                                             |

|    | 9.6                                                                                         | Override mode and test outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                                             |

|    |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                |

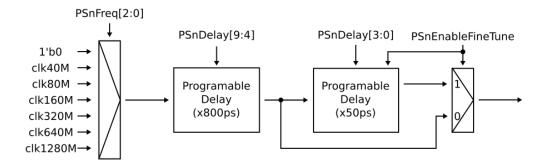

| 10 | Phase                                                                                       | a programmable clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                                                                                             |

| 10 |                                                                                             | e programmable clocks  Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>7</b> 9                                                                                                     |

| 10 | 10.1                                                                                        | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79                                                                                                             |

| 10 | 10.1<br>10.2                                                                                | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80                                                                                                       |

| 10 | 10.1                                                                                        | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79                                                                                                             |

|    | 10.1<br>10.2<br>10.3                                                                        | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80<br>80<br><b>81</b>                                                                                    |

|    | 10.1<br>10.2<br>10.3                                                                        | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80<br>80<br><b>81</b><br>82                                                                              |

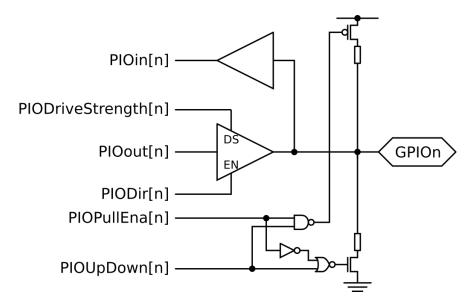

|    | 10.1<br>10.2<br>10.3<br><b>Gene</b>                                                         | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80<br>80<br><b>81</b><br>82<br>83                                                                        |

|    | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1                                                 | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80<br>80<br><b>81</b><br>82                                                                              |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3                                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79<br>80<br>80<br><b>81</b><br>82<br>83<br>83                                                                  |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3                                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters                                                                                                                                                                                                                                                                                                                                                                                                                                     | 79<br>80<br>80<br><b>81</b><br>82<br>83<br>83                                                                  |

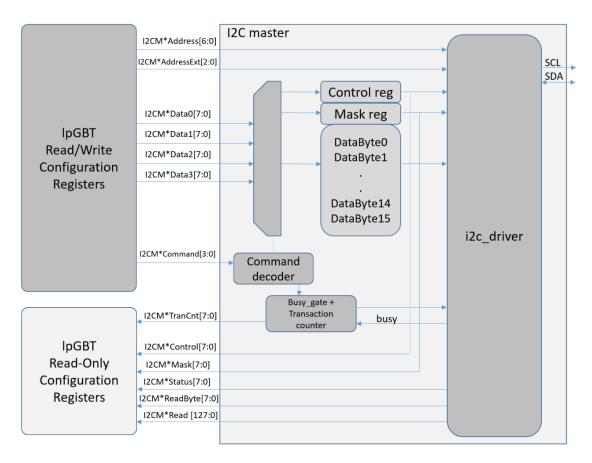

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> M                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters                                                                                                                                                                                                                                                                                                                                                                                                 | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85                                                                   |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> M                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters                                                                                                                                                                                                                                                                                                                                                               | 79<br>80<br>80<br><b>81</b><br>82<br>83<br>83<br>85<br>85                                                      |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> M                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register                                                                                                                                                                                                                                                                                                                                       | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89                                                       |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> M                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register                                                                                                                                                                                                                                                                                                                  | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90                                                 |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> M                 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.3 Status registers                                                                                                                                                                                                                                                                                          | 7980<br>8080<br>8182<br>833<br>838<br>8585<br>859<br>9090                                                      |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7980<br>8080<br>8182<br>8383<br>8585<br>85990<br>9090                                                          |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0)                                                                                                                                                                                                                                            | 7980<br>8080<br>8182<br>833<br>838<br>8585<br>859<br>9090                                                      |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0)                                                                                                                                                                                                                                            | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90<br>90<br>90<br>91                               |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.3 Status registers 12.C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1)                                                                                                                                                                                                                | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90<br>90<br>91<br>91                               |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.3 Status registers 12.C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1) 12.3.3 I2C_1BYTE_WRITE (0x2)                                                                                                                                                                                   | 7980808080808080808080808080808080808080                                                                       |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1) 12.3.3 I2C_1BYTE_WRITE (0x2) 12.3.4 I2C_1BYTE_READ (0x3) 12.3.5 I2C_1BYTE_WRITE_EXT (0x4) 12.3.6 I2C_1BYTE_READ_EXT (0x5)                                                                  | 7980808080808080808080808080808080808080                                                                       |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1) 12.3.3 I2C_1BYTE_WRITE (0x2) 12.3.4 I2C_1BYTE_READ (0x3) 12.3.5 I2C_1BYTE_WRITE_EXT (0x4) 12.3.6 I2C_1BYTE_READ_EXT (0x5) 12.3.7 I2C_1BYTE_RMW_OR (0x6)                                    | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90<br>90<br>91<br>91<br>92<br>92<br>93<br>93       |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1) 12.3.3 I2C_IBYTE_WRITE (0x2) 12.3.4 I2C_IBYTE_WRITE_EXT (0x4) 12.3.5 I2C_IBYTE_WRITE_EXT (0x4) 12.3.6 I2C_IBYTE_READ_EXT (0x5) 12.3.7 I2C_IBYTE_RMW_OR (0x6) 12.3.8 I2C_IBYTE_RMW_OR (0x7) | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90<br>90<br>91<br>91<br>92<br>92<br>92<br>93<br>93 |

| 11 | 10.1<br>10.2<br>10.3<br><b>Gene</b><br>11.1<br>11.2<br>11.3<br><b>I2C</b> N<br>12.1<br>12.2 | Phase-shifter operation Programming the phase-shifter channel Output configuration  ral Purpose I/O Configuring the Pin Reading the Pin Value Unconnected pins  Masters Input/Output signals of I2C masters Internal registers of I2C masters 12.2.1 Control register 12.2.2 Mask register 12.2.2 Mask register 12.2.3 Status registers 12C master commands 12.3.1 I2C_WRITE_CR (0x0) 12.3.2 I2C_WRITE_MSK (0x1) 12.3.3 I2C_1BYTE_WRITE (0x2) 12.3.4 I2C_1BYTE_READ (0x3) 12.3.5 I2C_1BYTE_WRITE_EXT (0x4) 12.3.6 I2C_1BYTE_READ_EXT (0x5) 12.3.7 I2C_1BYTE_RMW_OR (0x6)                                    | 79<br>80<br>80<br>81<br>82<br>83<br>83<br>85<br>85<br>89<br>90<br>90<br>91<br>91<br>92<br>92<br>93<br>93<br>93 |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 94              |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95              |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95              |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95              |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 96              |

|     | 10.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 96              |

|     | 12.4   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97              |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97              |

|     | 12.6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97              |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 97              |

|     |        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 98              |