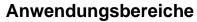

# Detektor Technologie und System Platform: Säule 1: Technologien für hochintegrierte Detektoren

# WP 3.1: 3D ASICS

### **Ulrich Trunk**

### **HGF Detector Portfolio Pillar 1 Meeting**

DESY, 13-14 June 2012.

# Outline: The "W(ish)"-List...

- > Why 3D-ASICS?

- > Where to start?

- > What do we want to achieve?

- > Who is part of the workpackage?

- > Who else will (or could) participate?

- > Which technologies and processes are available?

- > Which one will we use?

- What is the context in "Pillar 1" and the whole HGF Portfolio, and how can we gain from synergies?

- > What is our goal, i.e. final Deliverable and how will we achieve it?

# Why 3D-ASICS?

If you need to implement more circuit functionality in the same amount of chip area "real estate"\* you can...

- use a smaller technology node

- becomes very expensive

- will have a negative impact on analogue circuits

#### > use 3D-integraton

- TSVs

- Wafer bonding

- Limited availability

\*this is the usual challenge for pixelated detectors –why not start here?

A hypothetical example....

# Current State-of-the-art

Obviously with some existing pixel detector assembly...

| > AGIPD                                                           | Si, (Ge, GaAs)   | PS  | (DESY) |  |  |  |

|-------------------------------------------------------------------|------------------|-----|--------|--|--|--|

| <ul> <li>AGIPD 3D evaluation</li> </ul>                           |                  |     |        |  |  |  |

| > ATLAS Pixel                                                     | Si               | HEP | (DESY) |  |  |  |

| > CBM Pixel                                                       | MAPS             | HI  | (GSI)  |  |  |  |

| > Calice                                                          | Si, SiPMTs, MAPS | HEP | (DESY) |  |  |  |

| > CMS Pixel                                                       | Si               | HEP | (DESY) |  |  |  |

| LAMBDA/Medipix                                                    | Si, Ge, GaAs     | PS  | (DESY) |  |  |  |

| <ul> <li>Minapad (Single-Tier, Open-3D based assembly)</li> </ul> |                  |     |        |  |  |  |

| PANDA MVD/Topix                                                   | Si               | HI  | (GSI)  |  |  |  |

> .....many more....

Choice should be based on our final goal.....

# Disqualified as a goal due to an early start?

- > Minapad

- > AGIPD 3D evaluation

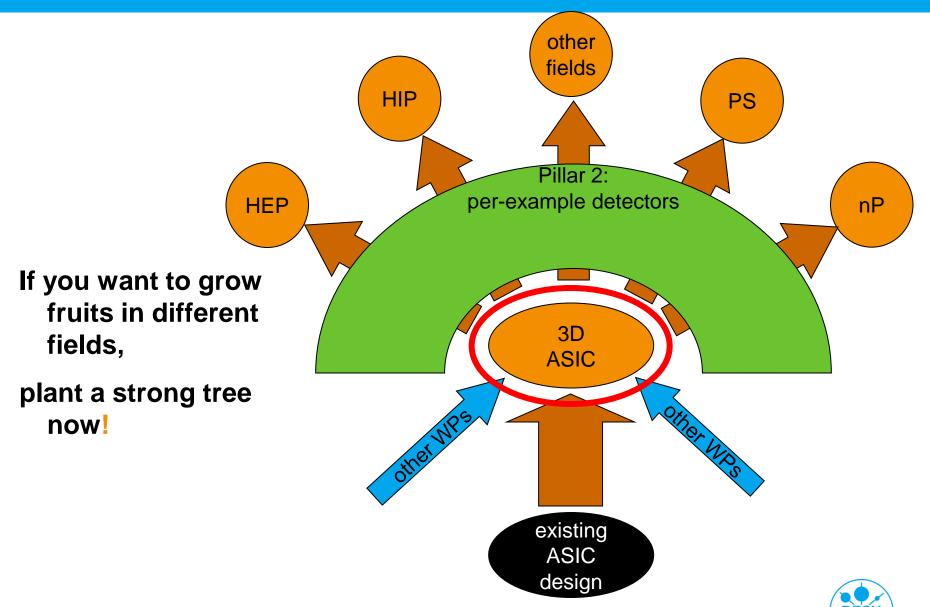

Enable any participating institution to produce 3D integrated circuits and detector assemblies by exploiting synergetic effects

- > among the participating Helmholtz-Centres and

- technologies coverd by the different workpackages:

- WP1-3 mixed signal ASICs

- WP1-4 high density interconnect

- WP1-2 3D and high-Z sensors

- WP1-5 novel materials

Stimulate spin-offs outside the pillar

- Tomographic dignostics of interconnects @ ANKA

- Integration of high-speed data transmission (Pillar 2)

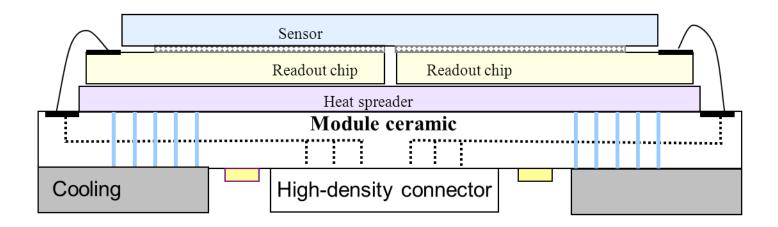

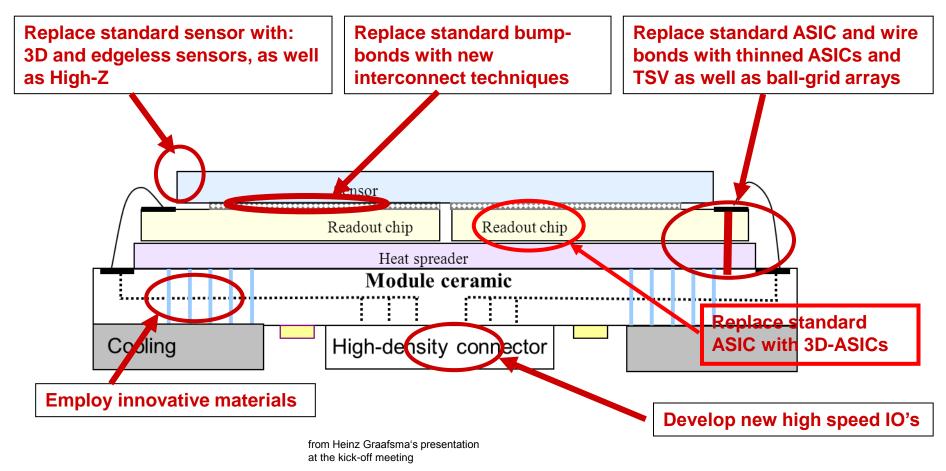

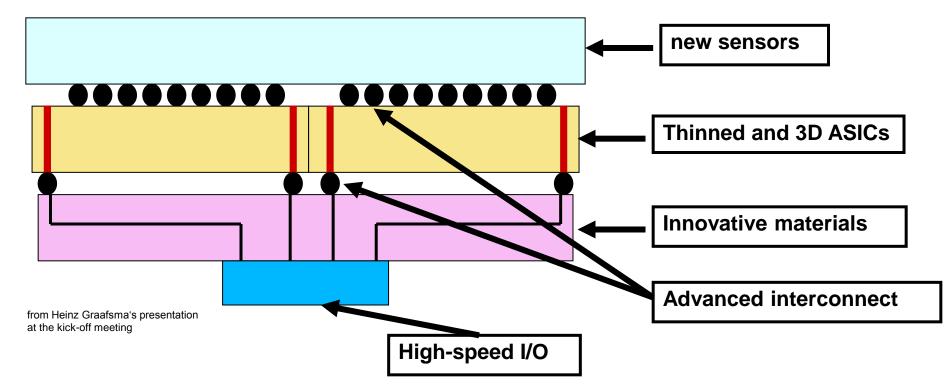

## Pillar 1 : The "Helmholtz-Cube"

#### **Vertically Integrated Detector Technology**

# Who is part of the workpackage?

Helmholtz-Centres:

- > DESY

- > FZJ

- > KIT

Karlsruher Institut für Technologie

# Who else will (or could) participate?

#### External research centres:

Fermi National Accelerator Laboratory (USA)

- IN2P3 Institut national de physique nucléaire et de physique des particules (France)

- Institut Pluridisciplinaire Hubert Curien, Strasbourg

- Laboratoire de l'Accélérateur Linéaire, Orsay

- Max-Planck-Institut für Physik, Munich

- Paul Scherrer Institut, Villigen PAUL SCHERRER INSTITUT (Switzerland)

- Science and Technology Facilities Council, STFC Technology, RAL, Harwell Oxford (UK) Science & Technology Facilities Council

University groups:

> AGH University of Science and Technology, Krakow,

- > Albert-Ludwigs-Universität Freiburg,

- RWTH Aachen,

- Technische Universität Dresden,

- Universitätsklinkum Carl Gustav Carus, Dresden

- > Universität Augsburg,

- Universität Bonn,

- **INFN** Florence,

- Universität Hamburg,

- Universität Heidelberg,

- Universität Wuppertal

# Other possible technology partners?

#### External partners:

Fraunhofer IZM

- > CERN

- > NIKHEF (NL)

- > VTT (FI)

# Which technologies and processes are available?

Full 3D integration:

- > CEA-LETI Open-3D (TSVs, microbump bonding

- CEA

- > IMEC ?

- > MIT Lincoln Lab

- > Tezzaron FaStack (TSVs, wafer bonding)

- MOSIS, CMP, FNAL

TSVs (Thru-Silicon Vias):

- Fraunhofer IZM / IST / EMFT / ENAS

- IBM (Micron/?)

- > AMS (?)

- > VTT (eniac/KET bridge)

- ST (eniac/KET bridge)

Bump-bonding:

Fraunhofer IZM / IST / EMFT

SEMICONDUCTOR

> Ziptronix

\_ \_ \_ \_

Which one to use?

-A**h**tark

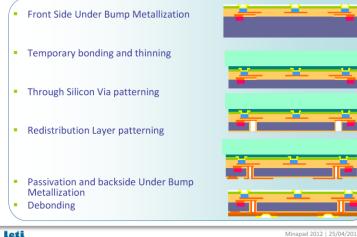

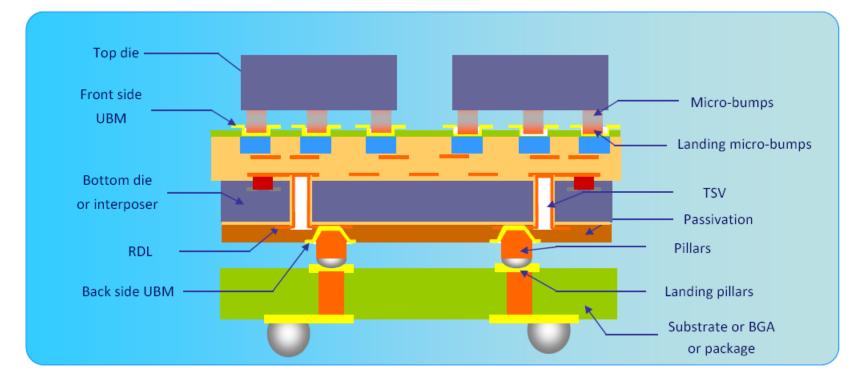

# CEA-LETI Open-3D Minapad – Medipix-based detector

#### **Process Flow description: TSV last technology**

Minapad 2012 | 25/04/2012 | 11

#### Main drawback: TSV size 60µm Ø

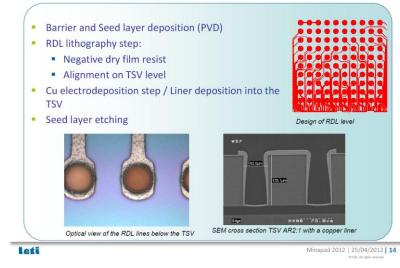

#### **Through Silicon Via (TSV) process**

- TSV lithography step: Double side step (Font side / back side alignment) Via Diameter=60µm DRIE Bosch 120µm Silicon etch: Etch rate~ 7.5µm/min Low undercut Slope = 90° Passivation oxide deposition x500 60.0,m SEM cross section of 120µm Temperature limited to 200°C TSV DRIE etched Step coverage = 20% Etch back: removal of the oxide layer at the bottom of the cavity Metal1 pad after oxide removal at the bottom of the via

Minapad 2012 | 25/04/2012 | 13

#### **Back Side signal redistribution**

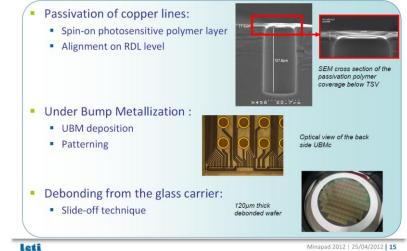

#### **Passivation and Under Bump Metallization**

Minanad 2012 | 25/04/2012 | 15

leti

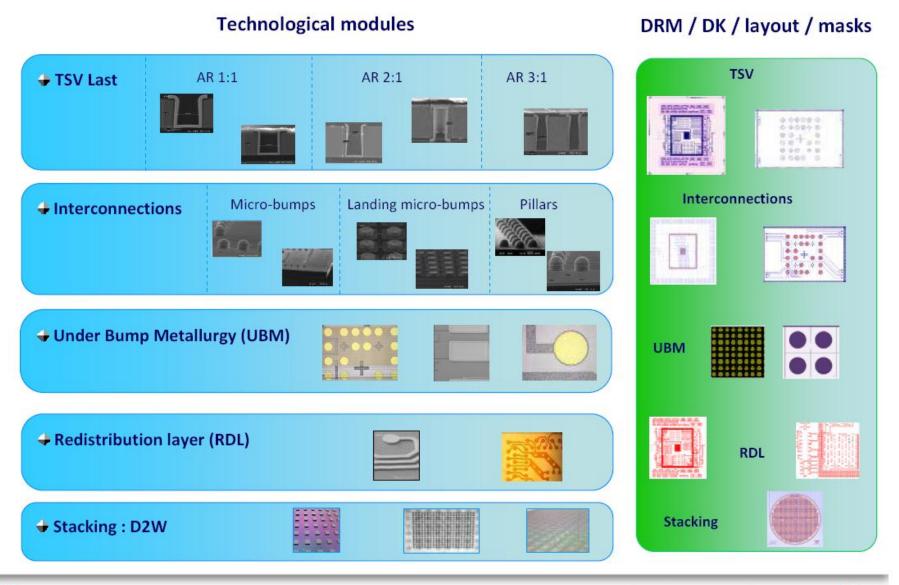

#### Open 3D<sup>™</sup> technological offer

#### Open 3D<sup>™</sup> technological offer

#### leti

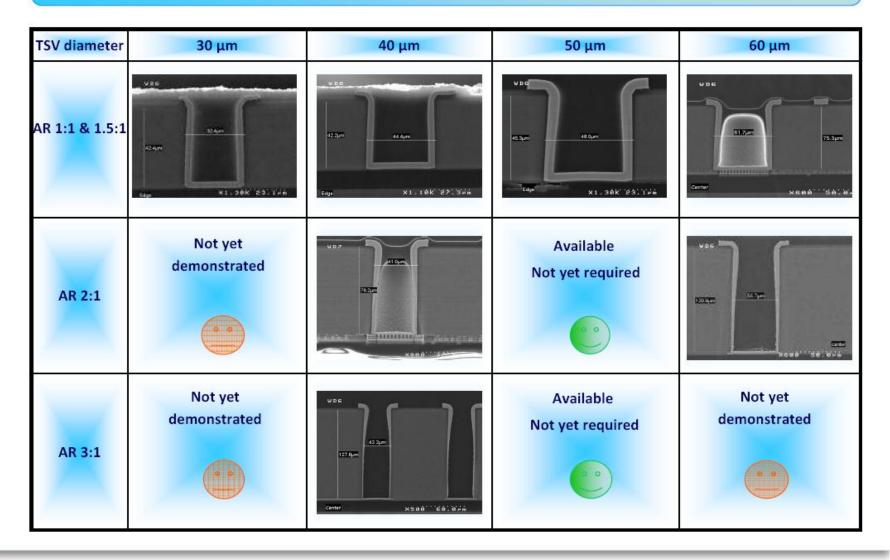

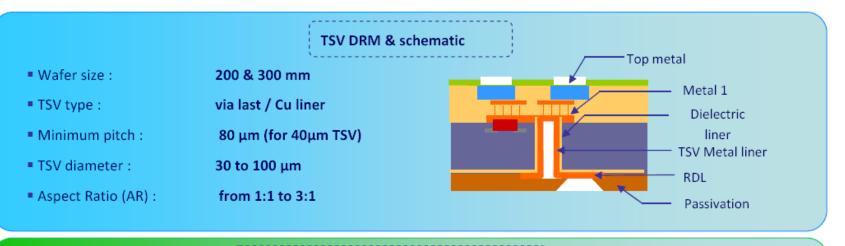

## Open 3D<sup>™</sup> technological offer / TSV

#### TSV Gallery

### Open 3D<sup>™</sup> technological offer / TSV

**TSV morphological & electrical results**

TS

AR 1:1

жseē'''dē.'e

AR 2:1

x500'''d0.'074

| 15V characteristics     |        |        |             |             |                                                          |  |

|-------------------------|--------|--------|-------------|-------------|----------------------------------------------------------|--|

| SV geometry             | R (mΩ) | C (pF) | Elec. Yield | Insul. (MΩ) | I <sub>leak</sub> (A)                                    |  |

| TSV <sub>60 / 80</sub>  | 15.1   | 0.57   | 100 %       | > 100       | -                                                        |  |

| TSV <sub>60 / 120</sub> | 19.1   | 0.82   | 100 %       | > 100       | 1.3 10 <sup>-9</sup> @ 10V<br>3.1 10 <sup>-9</sup> @ 50V |  |

| TSV <sub>40 / 80</sub>  | 20.1   | 0.46   | > 99%       | > 100       | -                                                        |  |

| TSV <sub>40 / 120</sub> | 30.4   | 0.63   | > 99%       | > 100       | 7.4 10 <sup>-9</sup>                                     |  |

|                         |        |        |             |             |                                                          |  |

TSV characteristics

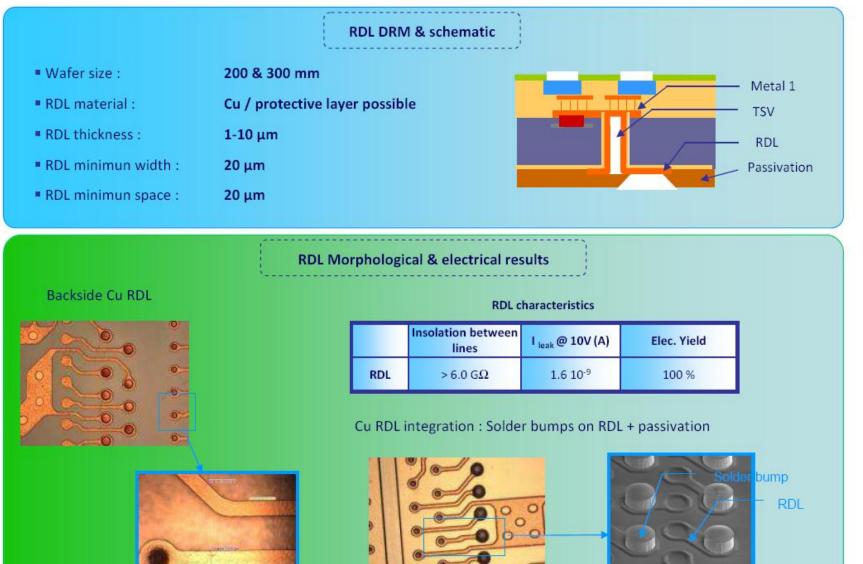

### Open 3D<sup>™</sup> technological offer / RDL

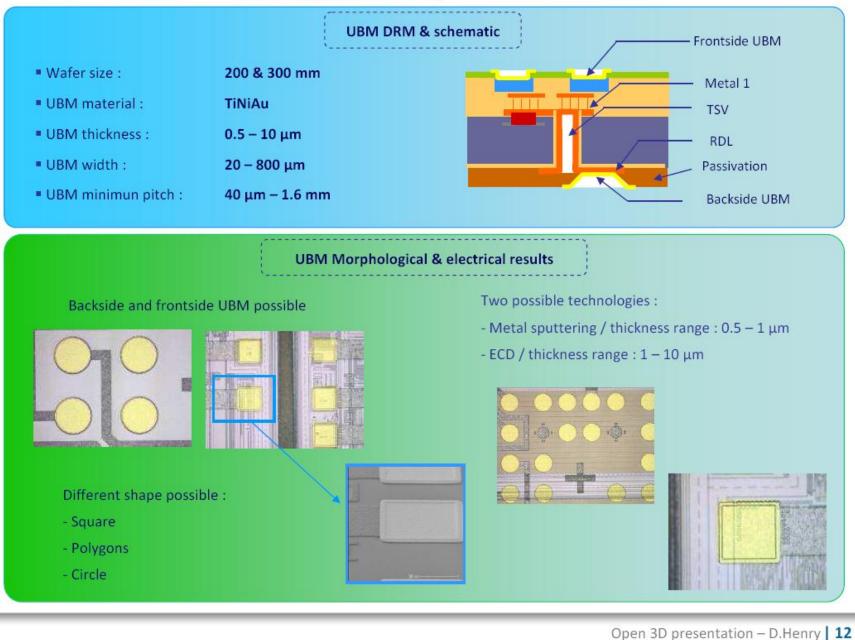

### Open 3D<sup>™</sup> technological offer / UBM

leti

© CEA. All rights reserved

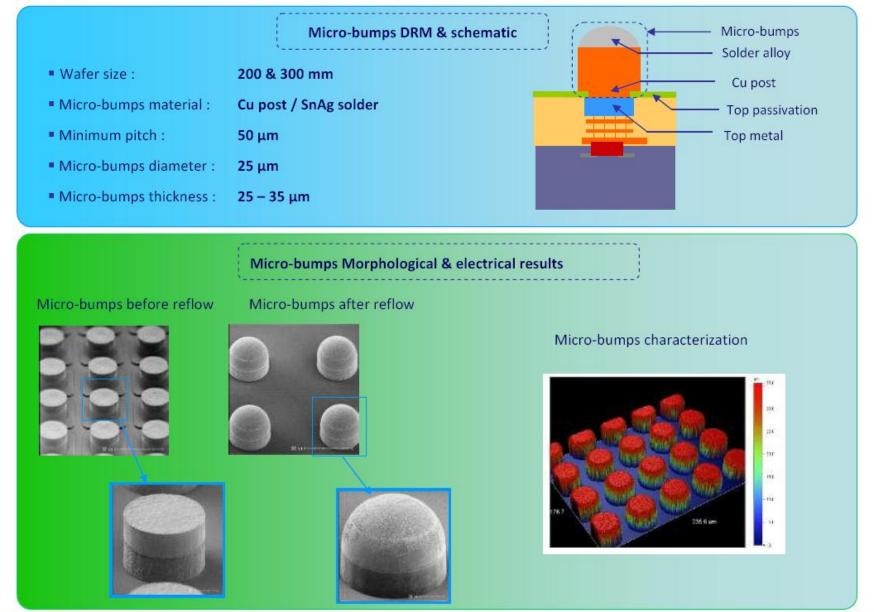

### Open 3D<sup>™</sup> technological offer / Micro-bumps

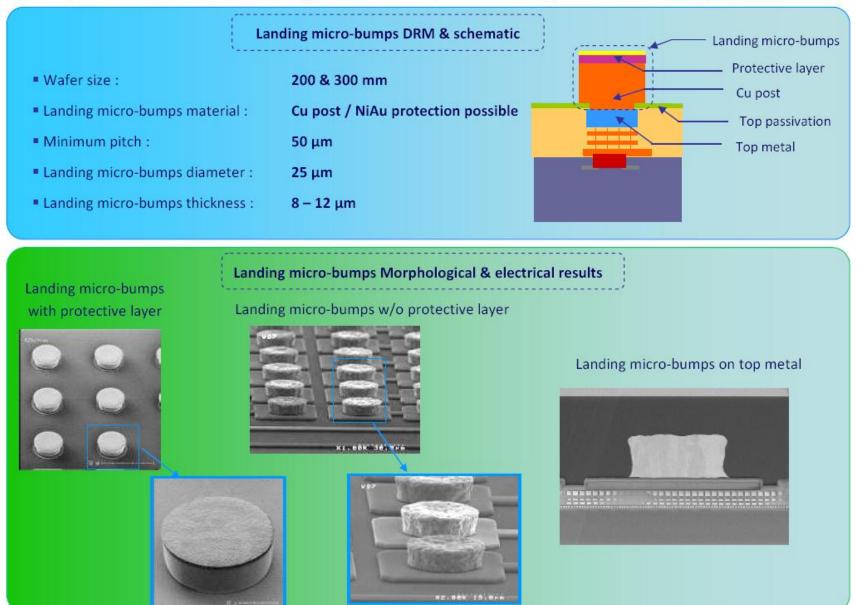

## Open 3D<sup>™</sup> technological offer / Landing micro-bumps

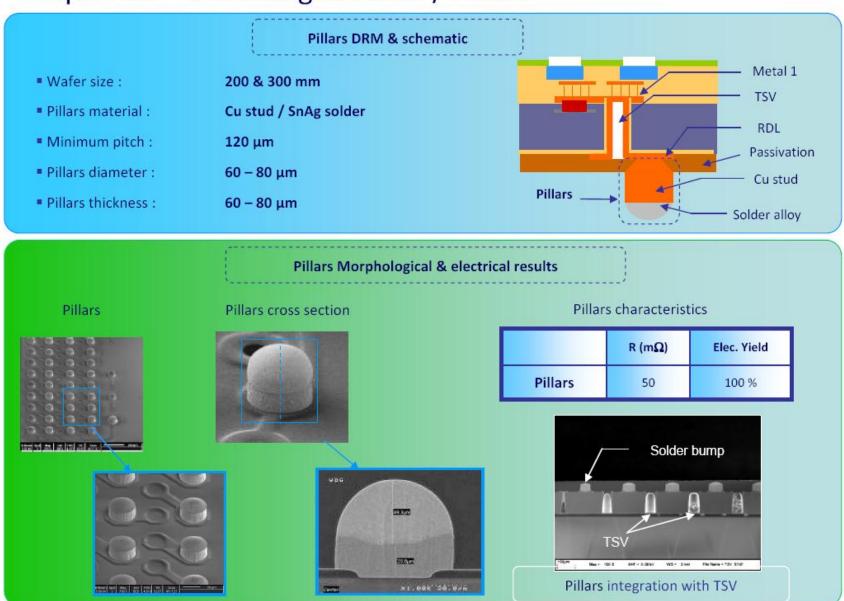

### Open 3D<sup>™</sup> technological offer / Pillars

OPEN

### **Tezzaron FaStack**

#### Products :: IC's Manufacturing :: CMOS 130nm FaStack(R)

| TECHNOLOGY:                 |                                                                                                                       | <u>=Fastack</u>              |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| CMOS 130nm FaStack (3D-IC I | Integration)                                                                                                          |                              |  |  |

| Met. layer(s):              | 6 per Tier (Metal 6 is used as bond interface) + TSV (Through Silicon Via)                                            | Main drawback:               |  |  |

| Poly layer(s):              | 1                                                                                                                     | Main Ulawback.               |  |  |

| Maximum die size:           | 2cm x 2cm                                                                                                             | Turne encoured delegate of   |  |  |

| Usable cells:               | 535 digital cells in both Low Power Low VT and Low Power Std VT                                                       | Turn-around delays of        |  |  |

| Available I/O:              | I/O cell library with digital pads is available for 1.2V/1.5V core 3.3V I/O, 5.0V To                                  |                              |  |  |

| Temp. range:                | -40° C. / +125° C.                                                                                                    | 0.5a 2a                      |  |  |

| Supply voltage:             | 1.2V/1.5V core 3.3V I/O, 5.0V Tolerant                                                                                |                              |  |  |

| SPECIAL FEATURES:           | High performance mixed analog/digital process. Two Tiers bonded face-to-face                                          |                              |  |  |

| APPLICATION AREA:           | Mixed Signals analog/digital, Pixels Arrays, Large Digital Designs, System on Chip                                    |                              |  |  |

| LIBRARIES:                  | Digital cells: All the standard digital cells plus composed cells (complex gates, arithmetic cells, register files,). |                              |  |  |

| Megacells:                  | Single Port RAM, Double Port RAM, ROM.                                                                                |                              |  |  |

| RAM/DP-RAM/ROM:             | Memory Compilers.                                                                                                     |                              |  |  |

| DESIGN KITS:                |                                                                                                                       |                              |  |  |

| Unix based:                 | CADENCE, SYNOPSYS, MENTOR, MicroMagic                                                                                 | Silicon<br>(thinned)         |  |  |

| Windows based:              | none                                                                                                                  |                              |  |  |

| PACKAGING:                  | All standard packages (DIL, LCC, PGA,).                                                                               |                              |  |  |

| TEST:                       | Contact CMP                                                                                                           |                              |  |  |

| INTERFACE FORMAT:           | GDSII, CADENCE                                                                                                        | يتلدي متعالدي متعالد ومتعالد |  |  |

| SPICE parameters:           | SPECTRE, HSPICE, ELDO                                                                                                 |                              |  |  |

| DRC, ERC rule set:          | Calibre DRC/LVS/3DLVS/PEX, Assura LVS/QRC, Hercules                                                                   | second a la diversion        |  |  |

| DESIGN SUPPORT:             | DRC checking (free for submitted designs)                                                                             |                              |  |  |

| PRICES:                     | Gate Poly                                                                                                             | rench Isolation)             |  |  |

| Cell libraries:             | Distributed upder NDA                                                                                                 | contact & vias) Silicon      |  |  |

| Design kits:                | Distributed under NDA                                                                                                 |                              |  |  |

| Prototyping:                | See the general CMP price list for prototyping                                                                        | s (M6, Top Metal)            |  |  |

| Low volume production:      | Depends on each specific case; contact CMP                                                                            |                              |  |  |

|                             |                                                                                                                       |                              |  |  |

-

3

/

TURNAROUND TIME:

Typical: TBD

Ulrich Trunk, Pillar 1 Meeting 2012 | Slide 25

## **Tezzaron FaStack**

#### Commercial from Tezzarons web site....

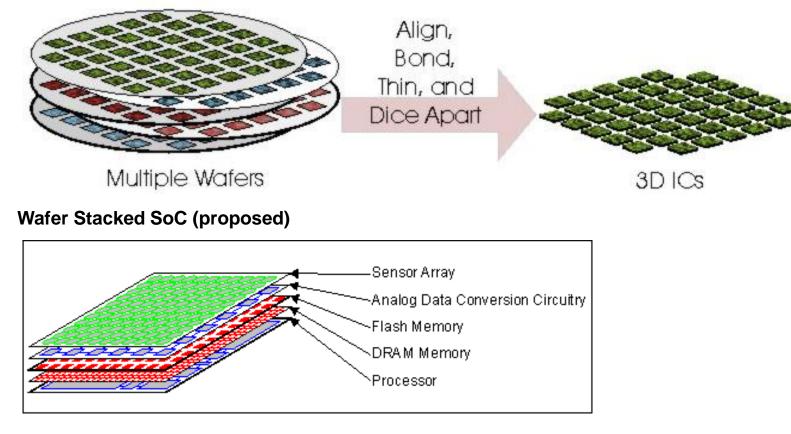

#### FaStack® Creates 3D Integrated Circuits (3D-ICs)

Tezzaron's groundbreaking FaStack technology creates fast, dense, highly integrated 3D chips. The heart of the process is wafer-level stacking. Device circuitry is divided into sections that are built on separate wafers using standard processing. Hundreds of thousands of vertical "Super-Contact<sup>™</sup>" connectors are built into the wafers. Finished wafers are metallized with a proprietary bonding pattern. They are then aligned with a precision of 0.5 micron, bonded, and thinned. Additional wafers may be bonded and thinned in turn. The finished stack is diced into individual 3D-IC devices.

#### Wafer Stacking

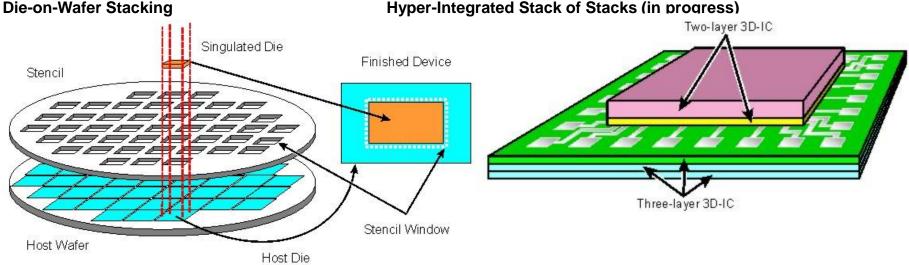

#### **Tezzaron FaStack**

#### Commercial from Tezzarons web site....

A variation on the FaStack process stacks individual dies onto an uncut wafer that is then diced into 3D-ICs. The dies may themselves be FaStack 3D-ICs, and the uncut wafer may be a FaStack wafer stack; this "stack of stacks" scenario allows for extremely flexible integration projects.

#### A Superior Technology

FaStack devices have many advantages over their single-layer counterparts. They are much more dense and their short vertical interconnects allow them to operate at higher speeds with a lower power budget. In addition, FaStack allows disparate elements to be processed on separate wafers for simpler production and greater optimization.

Unlike the separate chips in a "System-in-Package" (SiP) component, FaStack layers are fully integrated into a single IC by a dense system of through-silicon interconnects. FaStack devices match the tight integration of SoC devices while out-doing SiPs for high speed, low power budget, and tiny footprint.

Although other 3D-IC technologies exist, FaStack offers several important benefits:

- > No exotic process requirements

- > Extremely high interconnect density

- > High-precision alignment

- > Low-stress tungsten TSV for reduced thermal mismatch

- > No thin-wafer handling requirements

- > Extreme thinning allows 3D-ICs to fit in standard packaging

- > Real working devices since 2004 with **no** failures to date!

#### More commercials....

#### Applications for FaStack®

FaStack's wafer stacking offers benefits to a variety of applications. Sensor arrays, for example, achieve unprecedented density by moving the support circuitry to a different layer than the sensors themselves. "System-on-Chip" (SoC) devices built with FaStack reduce power consumption, footprint, and interconnect delays. Microprocessors built with FaStack incorporate a huge, fast memory cache on a separate layer. FaStack also enables enormous improvements in <u>memory technology</u> and allows seamless integration of differing process technologies. As 3D-ICs move into the mainstream, entirely new products will emerge to capitalize on this technology.

#### Getting the FaStack® Advantage

Tezzaron is currently exploiting the benefits of FaStack in three ways:

- 1) joint development projects with technology partners and systems designers,

- 2) licensing the production technology to manufacturers, and

- 3) producing our own FaStack-based products.

In the context of WP1 we could (and should) make use of:

- Mixed-signal ASICS (P1 WP2)

- "Aufbau und Verbindungstechnologien" (P1 WP4)

- "Innovative Detektorstruskturmaterialien" (P1 WP5)

- "Detektornahe optische Signalübertragung" (P2 WP3)

- > 3D- und "high-Z" sensors (P1 WP3)

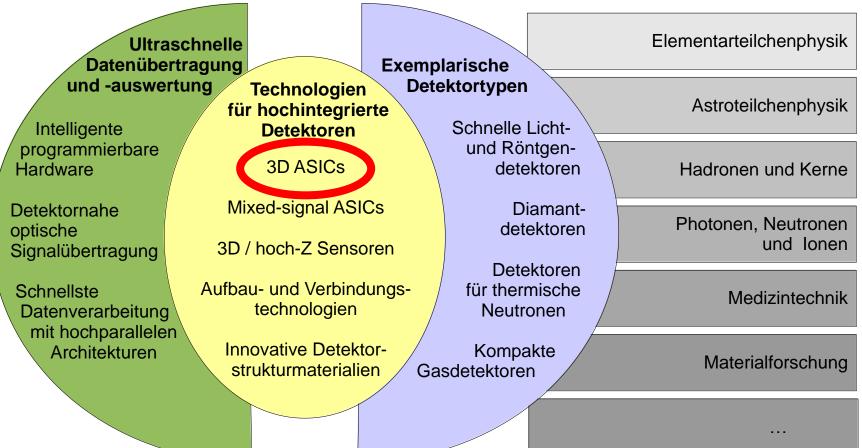

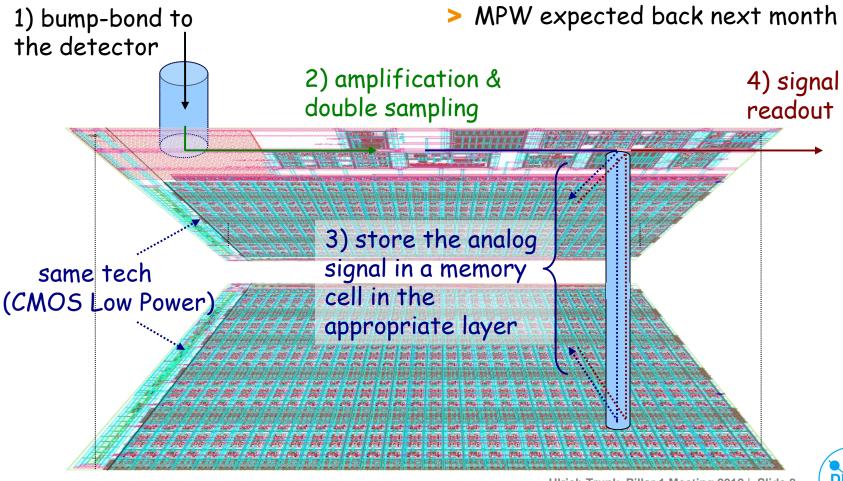

# What is our final goal, and how will we achieve it?

Proposal:

A 3D-integrated pixel readout ASIC which should be usable as a...

- Calorimeter readout in HEP

- trigger capability

- Tracker Readout in HEP and HI

- Iow radiation length

- trigger capability

- analogue information

### Imager Readout in PS

- photon counting

- charge integrating analogue information

## Outlook (i.e. my personal perspective of it)