#### **Timing and Fast Control @ ITIV**

#### Vladimir Sidorenko

Institute for Information Processing Technologies (ITIV)

#### KIT - The Research University in the Helmholtz Association

#### www.kit.edu

### **TFC - mission**

- (Re)synchronise data acquisition hardware with ~1 ns accuracy

- Perform system-wide flow control with round trip latency <10 us</p>

- Scalable >> 100 nodes

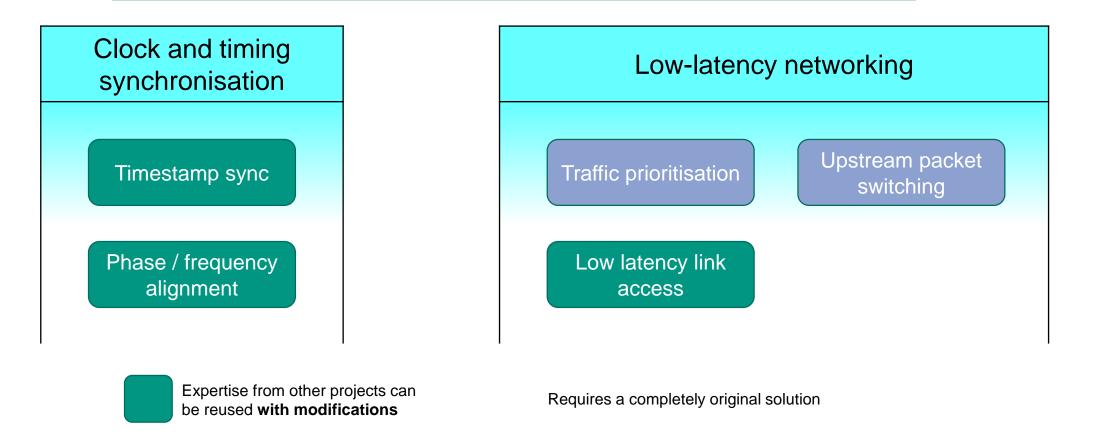

#### **Problem structure**

Bringing it all together in one architecture

3 Sep 16, 2021 Vladimir Sidorenko "Timing and Fast Control @ ITIV"

#### Features:

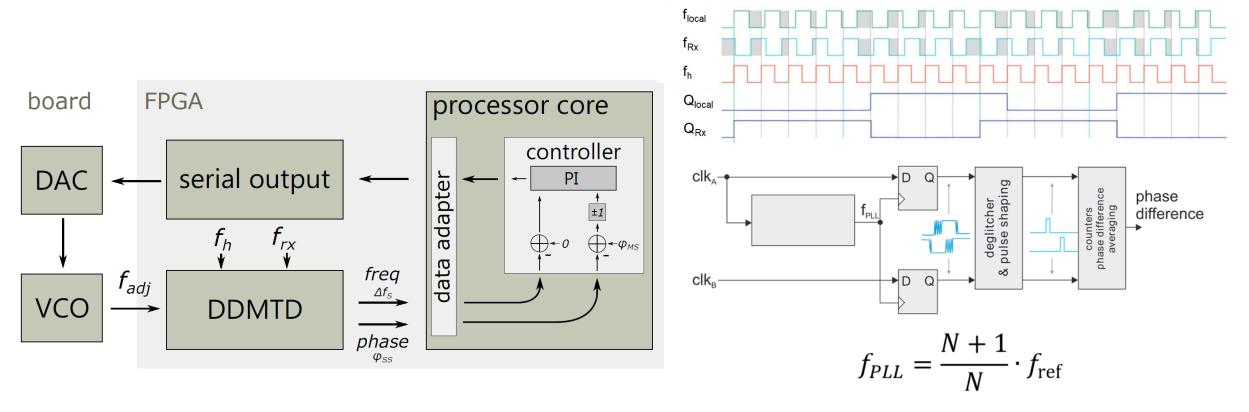

- Flexible Soft-PLL with accurate all-digital phase measurement

- Dual PI controller for parallel frequency and phase lock

## Platform: AFCK (Kintex-7)

### SoftPLL

# Allows for easy implementation of complex control algorithms in C

N = 8

# Karlsruhe Institute of Technology

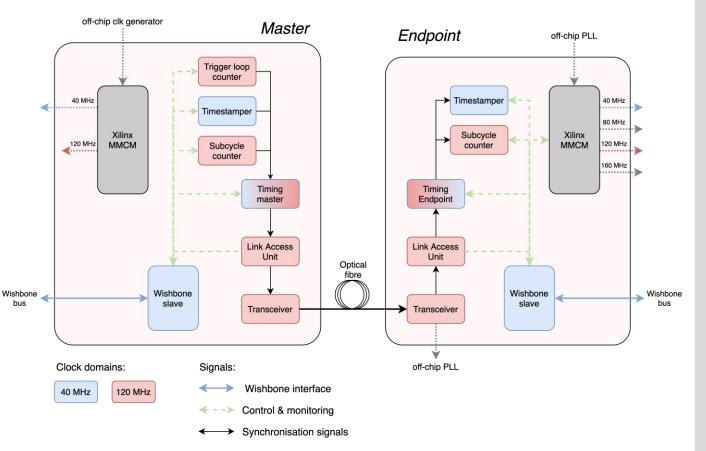

#### Features:

- Hard-PLL for frequency and phase alignment

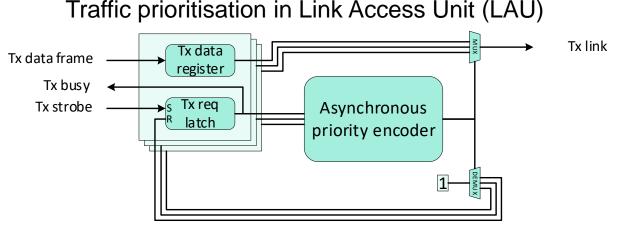

- Original link access unit design for prioritised link access with no dead time

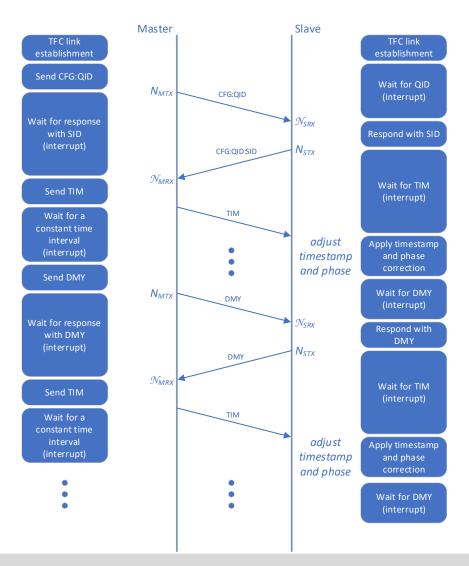

- Negotiation-based timestamp synchronisation (delay-compensated)

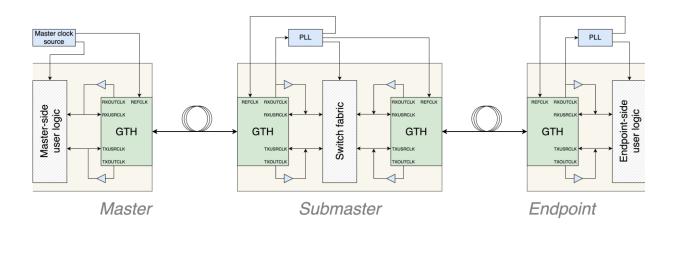

- Cascaded clock recovery

#### Prototype setup (Zynq-US)

#### Features:

- Hard-PLL for frequency and phase alignment

- Original link access unit design for prioritised link access with no dead time

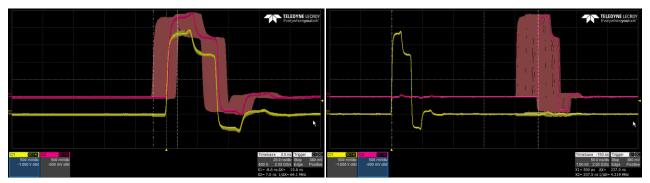

#### First synchronisation and latency measurements (latency ~ 200 ns)

## TFC1

- Timestamp broadcast scheme

- Cascaded clock recovery (hardware PLL)

- Rx and Tx FIFOs used

- Fully integrated into experimental infrastructure

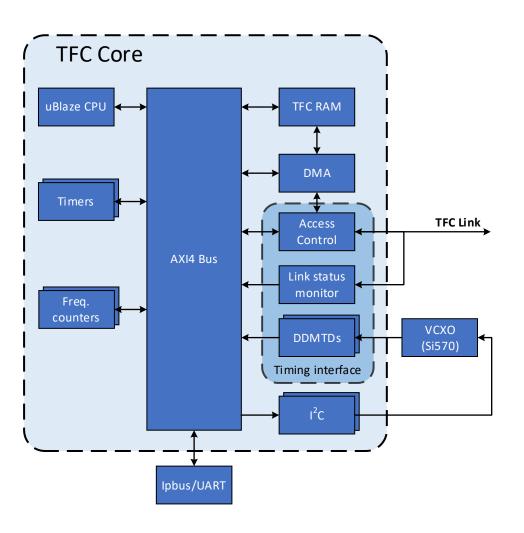

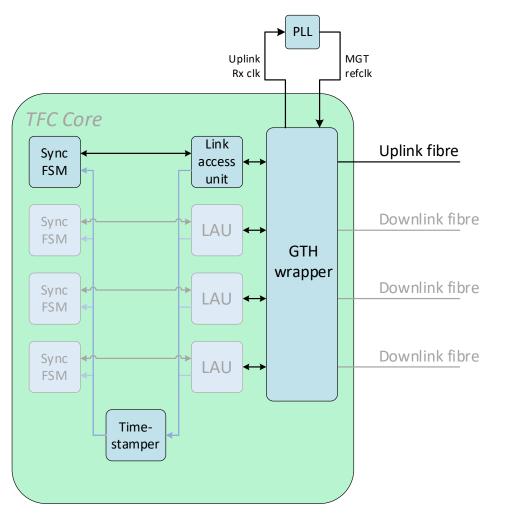

Prototype firmware architecture

Platform board: BNL-712 (Kintex-US)

TFC1

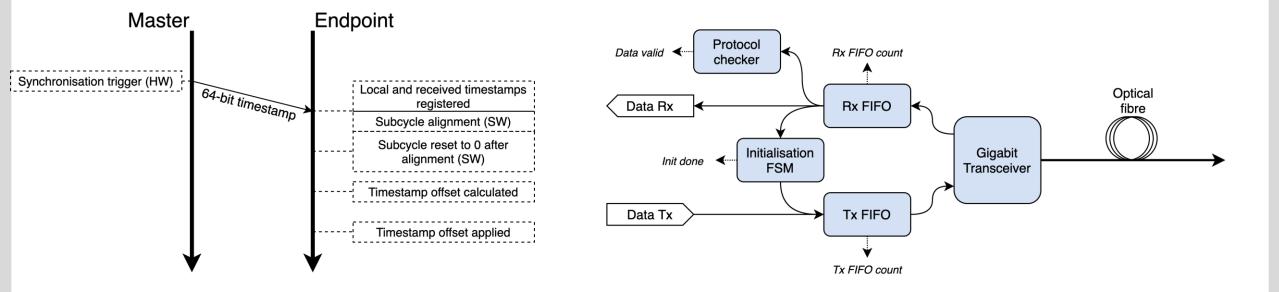

#### Timestamp synchronisation

#### Link access unit

## Next steps (global)

- GBT transport interface for out-of-box latency optimisation and determinism

- Integrate negotiation-based timestamp synchronisation

- Evaluate TClink for fine phase shift tuning

# BACKUP

12 Sep 16, 2021 Vladimir Sidorenko "Timing and Fast Control @ ITIV"

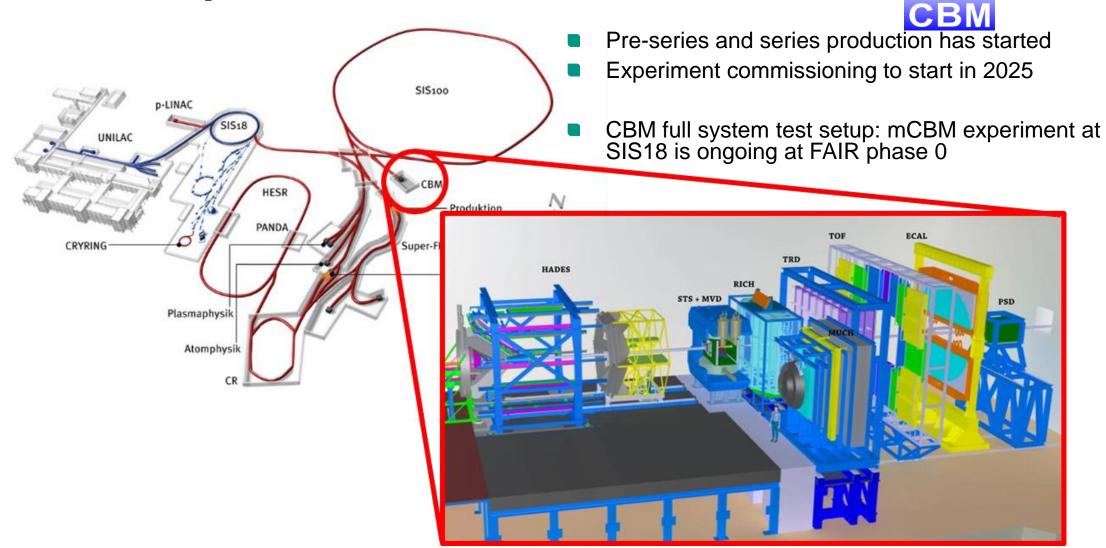

### **CBM Experiment @ FAIR**

**13** Sep 21, 2021

Vladimir Sidorenko on behalf of CBM collaboration "Prototype Design of a Timing and Fast Control system in the CBM Experiment" for TWEPP2021

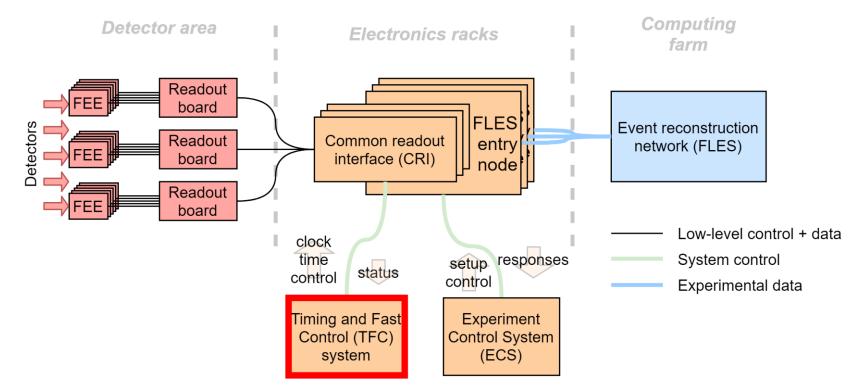

### **Data Acquisition System**

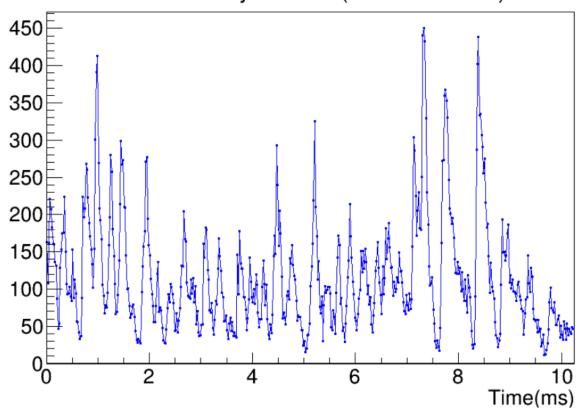

- Free-running DAQ (1 TB/s expected)

- Self-triggered timestamping front-end

- Occasional experimental data spikes

Throttling (study done by X. Gao):

Versatile fast control network required Beam intensity structure (resolution: 20 us)

Vladimir Sidorenko on behalf of CBM collaboration "Prototype Design of a Timing and Fast Control system in the CBM Experiment" for TWEPP2021

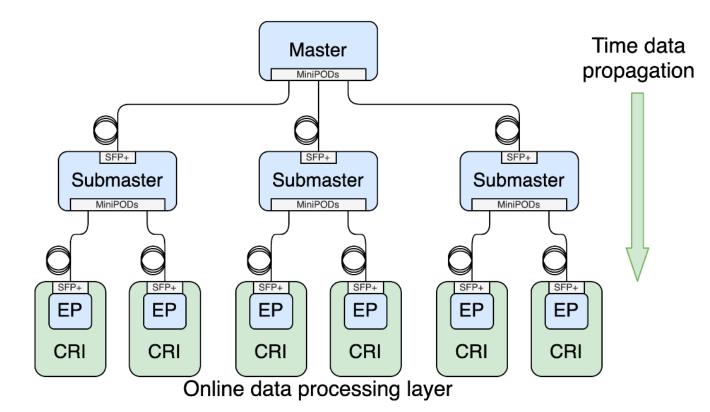

## Topology

15 Sep 16, 2021 Vladimir Sidorenko "Timing and Fast Control @ ITIV"

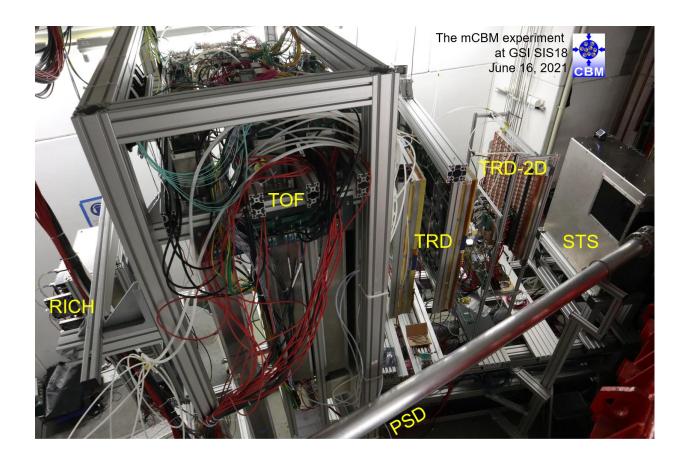

### **TFC1 beam test**

#### **TFC1** beam test

hTrd2dPsdDiff Counts 3500 Entries 206276 -202.5Mean Std Dev 1725  $\chi^2$  / ndf 377.7 / 34 3000 p0 2976 ± 27.8 p1  $-1801 \pm 0.3$ p2  $38.23 \pm 0.30$ p3  $398.2 \pm 4.5$ 2500 2000 1500 1000 500 The share the Alex lown more and the thread again by -3000-2000 -1000 0 1000 2000 3000 time diff [ns]

Trd2d - Psd time difference